# 超低消費電力型光エレクトロニクス実装システム 技術開発プロジェクト - デバイス・実装基盤技術 -

2022年2月10日

技術研究組合光電子融合基盤技術研究所 中村 隆宏

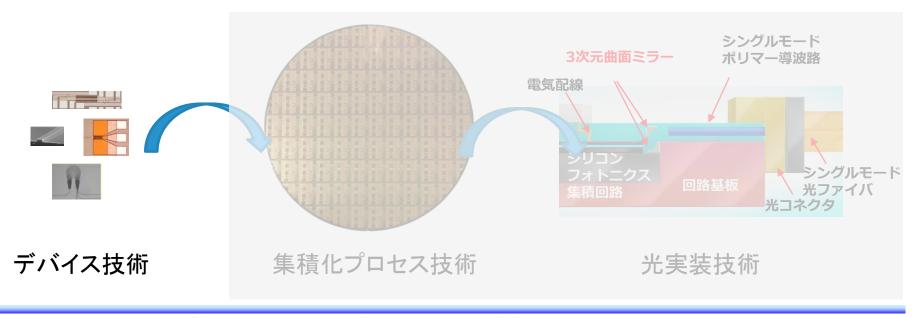

# 光電子集積インタポーザの必要性

- 10Tbpsを可能にするには光電子集積インターポーザが必要

- 特に、光実装技術、光接続技術が大きな課題

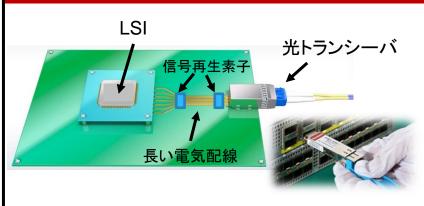

# 光トランシーバ(従来方式)

- 長い電気信号配線(~50cm)

- → ノイズ、遅延などによる信号劣化

- 信号再生素子が必要

- → 消費電力増

- 🖂 コネクタ数増大

- → コスト増

LSIの外部I/O:数Tbps程度で限界

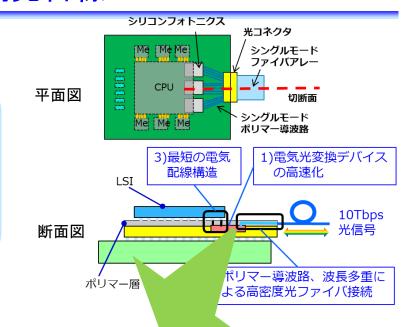

#### 光電子集積インターポーザ

- 短い電気配線(<50mm)</p>

- → 高速信号伝送可能

- ② 信号再生素子が不要

- → 低消費電力

- ② 光再配線

- → コネクタ数減によるコスト低減

- 🙁 光実装技術、光接続技術が未成熟

LSIの外部I/O:10Tbps以上可能

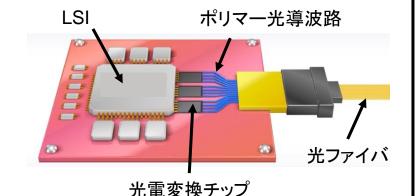

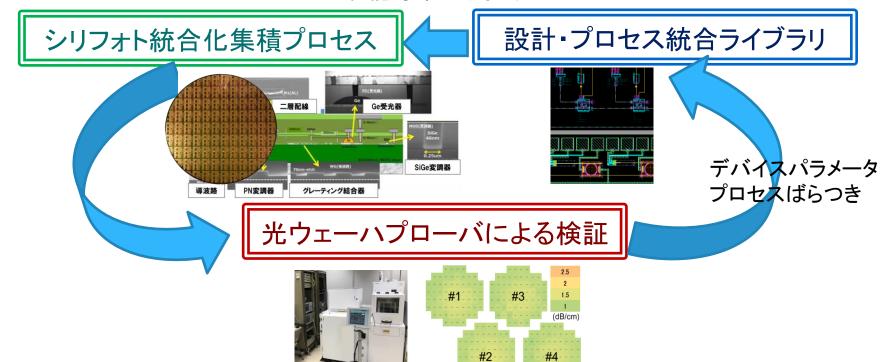

# 光電子集積インタポーザの基盤技術

- 光電子集積インターポーザは、大容量伝送のみでなく、低消費電力、小型・低コストも同時に求められる

- これら全要素を満たす基盤技術(デバイス、集積化プロセス、光実装)を開発する

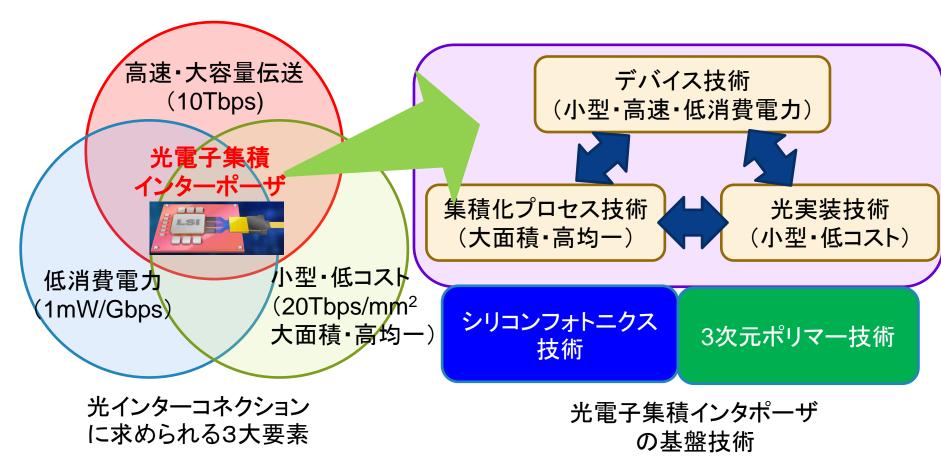

# 10Tbps達成の内訳とデバイス・実装技術開発目標

# 光電子集積インターポーザ

1 シリコンフォトニクスチップ当たり 112Gbps×16波×送受(2) = 3.6Tbps

1 LSI当たり 3シリコンフォトニクスチップで、  $3.6 \text{Tbps} \times 3 = 10 \text{Tbps}$

#### 第一期の技術目標第二期の技術目標第三期の技術目標

| デイ・プセ技開  | 高速デバイス           | 25Gbps/Si変調器                                              | 50Gbps/PAM4                  | 112Gbps/56GBaud+PAM4                                |

|----------|------------------|-----------------------------------------------------------|------------------------------|-----------------------------------------------------|

|          | 低電力デバイス          | 5mW/Gbps /Si変調器                                           | 3mW/Gbps /<br>高性能材料(SiGe)変調器 | 1mW/Gbps /<br>小型電界吸収型SiGe変調器                        |

|          | 波長多重デバイス         | 4波長/アレイ導波路型<br>回折格子(AWG)(素子)                              | 8波長/AWG(素子)                  | 16波長/AWG+バンドパスフィルタ<br>(集積回路)                        |

| 実装 技術 開発 | 光の入出力<br>(広帯域密度) | 10 μ mレベル目合わせ精度/<br>グレーティングカプラ+縦型ポリマー導波路<br>(0.5Tbps/mm²) |                              | 1 μ mレベル目合わせ精度/<br>3次元ミラー+横型ポリマー導波路<br>(20Tbps/mm²) |

|          | 電気配線構造           | 平面構造                                                      |                              | インターポーザ構造                                           |

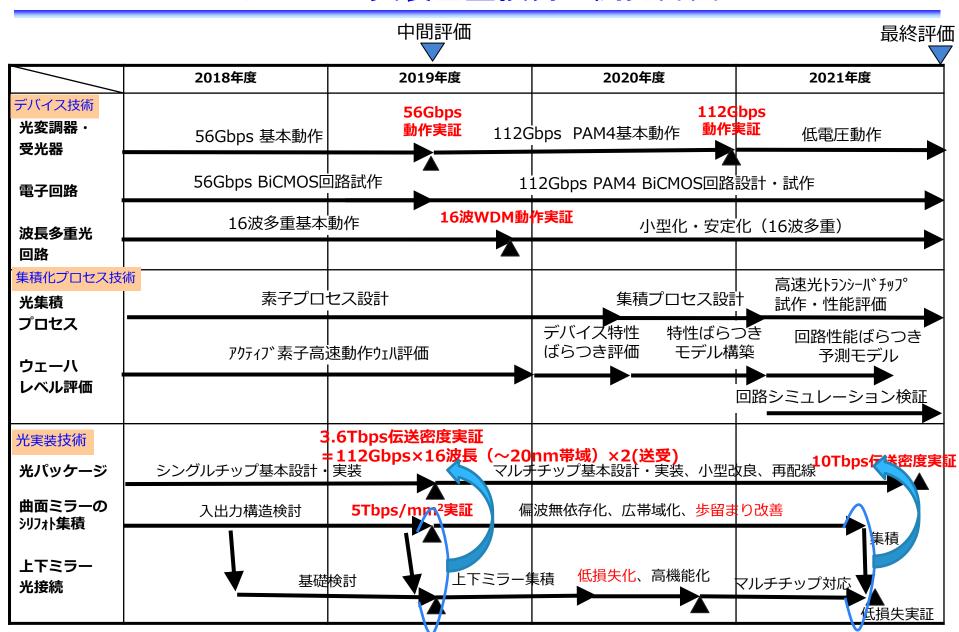

# デバイス・実装基盤技術の開発計画

# デバイス技術

# デバイス技術の開発目標

#### デバイス技術

#### 最終目標:

- ·112Gbps光素子·電子回路基本動作

- •16波長合分波した光信号のシングル モードファイバ伝送

- •1mW/Gbps以下の素子特性

#### 超小型·大容量波長多重(WDM)光回路

3.6Tbps(112Gbps×16波×送受)×3チップ≒10Tbps

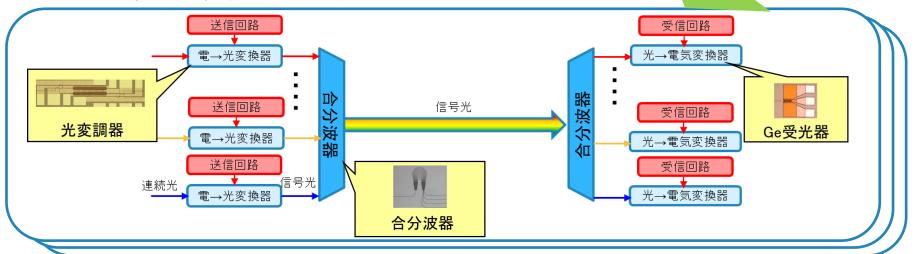

# 光変調器・受光器のアプローチ

#### デバイス技術

- 波長多重によるスケーリング可能、且つ、低消費電力・高速伝送を実現する光変調器・ 受光器を開発

- ⇒小型・低容量のGeSi電界吸収(EA)型光変調器/受光器が有利 特徴として、狭幅選択Ge成長を用てC、L帯波長を1チップ集積化可能(13Tbps以上)

#### Si光変調器の比較

| GeSi電界吸収<br>(EA)型光変調器 |           | Siマッハツェンダー(MZ)<br>型光変調器 | Siリング型光変調器              |

|-----------------------|-----------|-------------------------|-------------------------|

|                       | L         |                         | Δλ(V)                   |

| サイズ                   | ~50µm     | >1mm                    | ~5µm                    |

| 高速性                   | ~100Gbps  | ~90Gbps                 | ~56Gbps                 |

| 消費電力                  | <1mW/Gbps | <3mW/Gbps               | <1mW/Gbps               |

| 温度依存性                 | 25~85°C   | 温度無依存                   | <1℃<br>(温調必須)           |

| WDM帯域                 | C,L带      | 波長無依存                   | <1nm<br>(温調 <b>必</b> 須) |

第3期

第1,2期

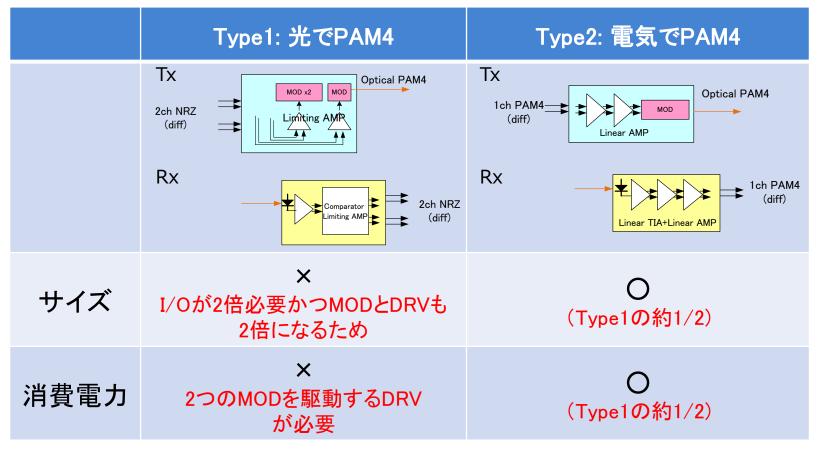

# 光変調器・受光器の駆動電子回路のアプローチ

#### デバイス技術

- 112Gbps PAM4のTx/Rxの方式とIC構成を検討

- 小型化、低消費電力化には電気でPAM4(Type2)が有利 →実証コストの点からSiGe-BiCMOSが有利

- PAM4に必要なLinear AMPの112Gbps PAM4動作を回路設計・試作にて検証

112Gbps PAM4のTx/Rx方式

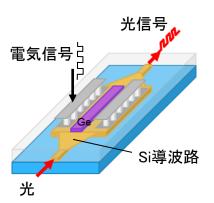

# 高速光変調器

#### デバイス技術

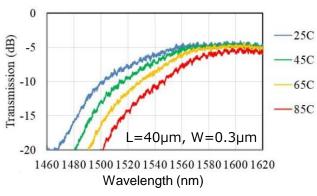

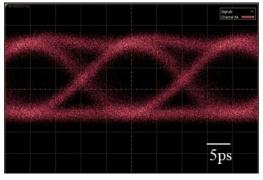

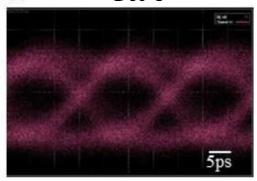

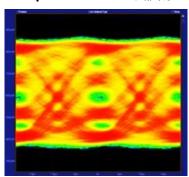

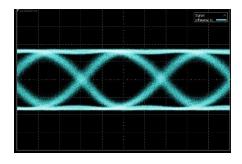

- ■ドーピングと素子形状最適化により70GHz以上の周波数帯域、56Gbpsアイ波形確認

- ■高温85°Cにおいても56Gbps動作可能

- ■112Gbps-PAM4電気信号での直接駆動により光信号出力を実証

GeSi-EA光変調器構造

EO周波数応答特性

光透過特性の温度依存性

56Gbps NRZ (PRBS 2<sup>31</sup>-1)アイ波形 @25°C @85°C

ER=3.2dB, IL  $\sim$  4dB @2.5Vpp L=40  $\mu$  m, W=0.3  $\mu$  m

ER=2dB, IL  $\sim$  8dB @2.5Vpp L=40  $\mu$  m, W=0.3  $\mu$  m

112Gbps-PAM4アイ波形@25°C

TDECQ 1.69 dB (PRBS 2<sup>13</sup>-1)

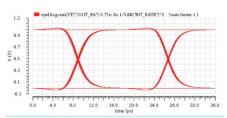

# 光変調器ドライバー

#### デバイス技術

**INP**

INN

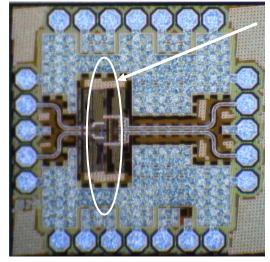

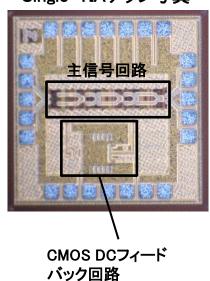

- 電界吸収型光変調器ドライバーを試作・評価

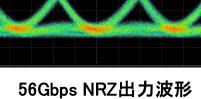

- ●最先端SiGe-BiCMOSプロセスを用いて、高線形動作回路設計により、56Gbps NRZ、 112Gbps PAM4の電気出力波形を確認

- ●高振幅・低ジッタ化回路を設計し、2Vppを達成

IC内広帯域インピー ダンス整合 (多重反射を抑制、 高品質な出力波形)

OUT

単相振幅 1Vpp(50Ω終端)

112Gbps PAM4出力波形PN31 単相振幅 1Vpp(50Ω終端)、光変調器負荷で2Vpp

電界吸収型光調器ドライバーチップ写真

電界吸収型光変調器ドライバーを試作・評価し、112Gbps PAM4の出力波形を確認

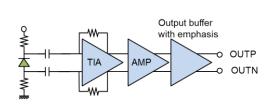

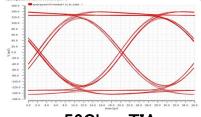

# 受光器トランスインピーダンスアンプ(TIA)

#### デバイス技術

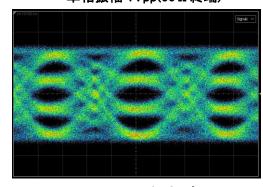

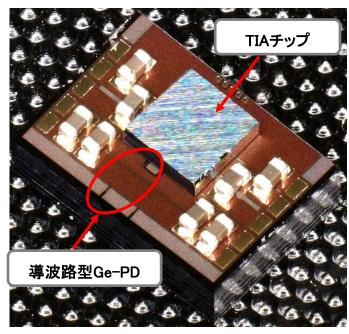

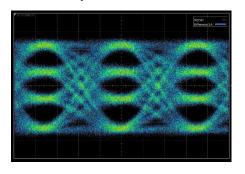

- SiGe-BiCMOSで試作したTIAと導波路型Ge-PDをFlip Chip実装してRxを作製

- 56Gbps NRZ及び112Gbps PAM4光入力の電気特性を評価

- Single-PD方式TIA搭載Rxで良好な56Gbps動作を実証

- 更に、112Gbps PAM4の出力波形を確認

Single-PD方式TIA搭載RX

#### Single-TIAチップ写真

56Gbps RX出力波形

112Gbps PAM4 RX出力波形 I<sub>PD</sub>=410μA<sub>bb</sub>

TIAを試作・評価し、Flip Chip実装したRxで良好な56Gbps及び112Gbps PAM4動作を実証

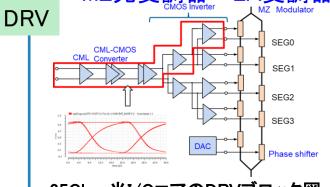

# CMOSを用いた1mW/Gbps低消費電力化

#### デバイス技術

- CMOSの設計環境を構築。22/12nm CMOSのPDK入手

- DRVの出力段CMOS Inverter構成で消費電力の解析

MZ光変調器→EA変調器、SEG数4→1、駆動振幅1.8→1Vpp

| 25Gbps      | 56Gbps      |

|-------------|-------------|

| MZ変調器DRV    | EA変調器DRV    |

| (28nm)      | (22nm)      |

| 2.15mW/Gbps | 0.27mW/Gbps |

25Gbps光I/OコアのDRVブロック図

56Gbps EA変調器DRV 出力波形 1Vpp

- 22nm CMOS(SOI)のPDKで、56Gb/s TIAの解析

- AC Coupling方式3段で、動作速度56Gbps、消費電力36.7mWを解析で実現

TIA

22nm CMOS TIAブロック図

56Gbps TIA 出力波形 差動480mVpp

| 25Gbps<br>TIA<br>(28nm) | 56Gbps<br>TIA |

|-------------------------|---------------|

| 3.52mW/Gbps             | 0.66mW/Gbps   |

22nm CMOSを用いて1mW/Gbpsを解析し、DRVで0.27mW/Gbps、TIAで0.66mW/Gbps、DRV+TIAで1mW/Gbpsの低消費電力化を達成

# 波長多重光回路

**DMZI** for TE

Crossing

#### デバイス技術

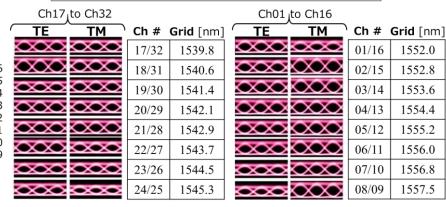

### ■ 16 λ 波長多重回路を作製・評価

- ▶受信向け任意偏波対応

- ▶動作波長: Cバンド帯域

- ▶シリコン細線型パッシブデバイス

- ▶サイズ: 1.7 × 2.8 mm²

- ▶信号対クロストーク/チャネル

- ✓ 8 λ -AWG内: -20~-24dB ✓ 2 λ -DMZI内: -26~-34dB

# Output DMZI for TM Ch 01-08 for TE ( $\lambda$ 1- $\lambda$ 8) Ch 09-16 for TM ( $\lambda$ 1- $\lambda$ 8) Ch 17-24 for TE ( $\lambda$ 9- $\lambda$ 16) Ch 25-32

16 λ 波長多重回路の構造図

#### 16λ波長多重回路の計測スペクトル特性

#### Ch17~Ch32 Ch01~Ch16 Solid line: TE mode Transmittance [dB] -10 -20 -30 -40 Dotted line: TM mode Ch17, Ch32 — Ch01, Ch16 Ch18, Ch31 — Ch02, Ch15 — Ch19, Ch30 —— Ch03, Ch14 — Ch20, Ch29 —— Ch04, Ch13 — Ch21, Ch28 — Ch05, Ch12 — Ch22, Ch27 - Ch06, Ch11 — Ch23, Ch26 —— Ch07, Ch10 — Ch24, Ch25 - Ch08, Ch09 1540 1545 1550 1555 1560 Wavelength [nm]

#### 32Gbps NRZ変調信号の伝送特性

AWG for  $\lambda 9 - \lambda 16$

任意偏波の16波長のWDM光信号を合分波可能な小型波長多重回路を実証

for TM ( $\lambda 9 - \lambda 16$ )

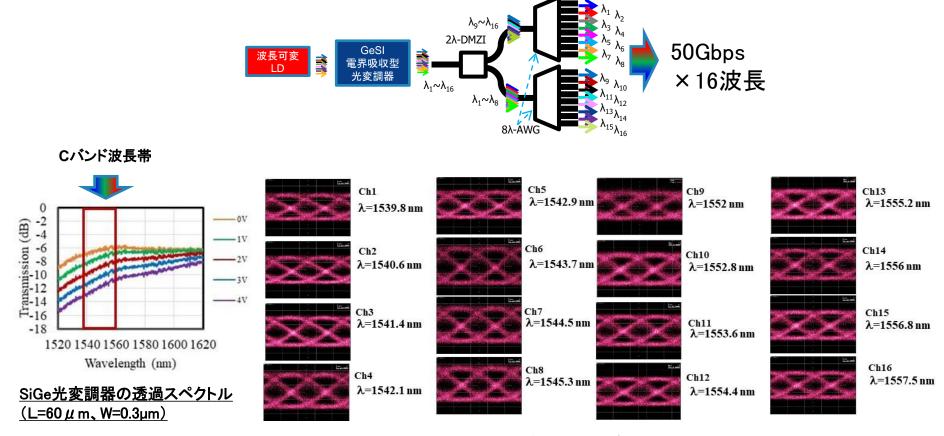

# 高速光変調器+16波長多重光回路

#### デバイス技術

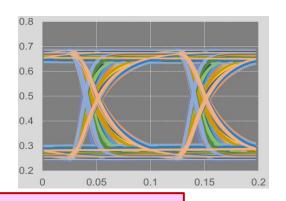

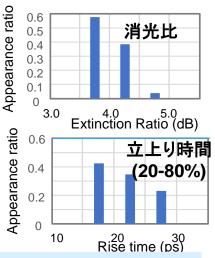

<u>50Gbps×16波長 アイパターン</u> 消光比4~4.4dB@2.5Vpp

GeSi電界吸収型光変調器を用いて、50Gbps動作×16波長動作@Cバンド波長帯を実証

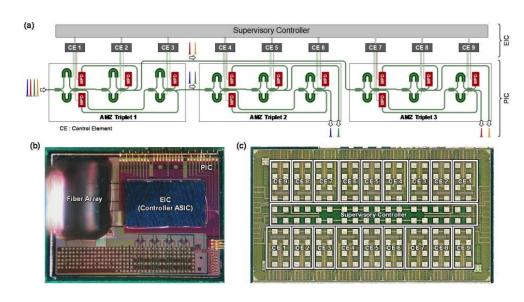

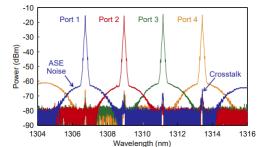

# 次世代温度耐性波長多重光回路

#### デバイス技術

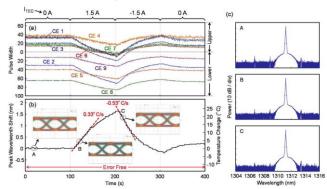

- 非対称マッハツェンダーに光モニタとヒーターによるフィードバック制御を導入し位相エラーを 自動訂正。クロストーク-50~-60dB@4波長を実現。(シミュレーションでは64波長可能)

- 更に、温度変化に対しフィードバック制御可能な電子回路を集積した耐温度・クロストークフリーの波長多重光回路を実現

- 急激な温度変化(少なくとも0.53°C/s)に対して4ch 25Gbps信号で各波長分波後、エラーフリーを実現

CAT (Cascaded AMZ Triplets)構造を持つ波長分波回路 と電子制御回路

各波長の光出カスペクトル

温度変化に対する光出カスペクトル及び アイパターンの変化

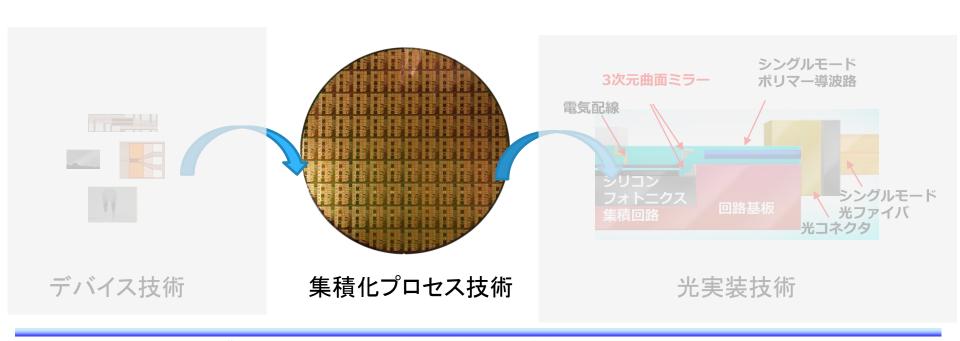

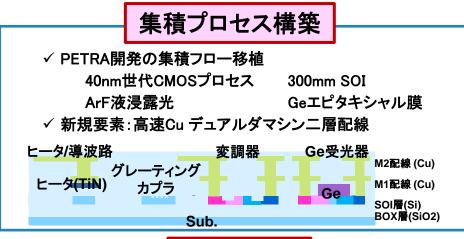

# 集積化プロセス技術

# 集積化プロセス技術の開発目標とアプローチ

#### 集積化プロセス技術

最終目標: 10Tbps/ノード光電子集積インターポーザに向けた集積プロセス構築

シリフォト集積プロセス技術の300mm一貫試作ファンドリへの展開

介

アプローチ:シリフォト統合化集積プロセス & 設計・プロセス統合ライブラリ技術確立

#### 性能・歩留まり予測

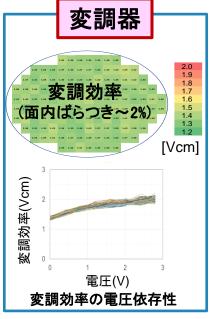

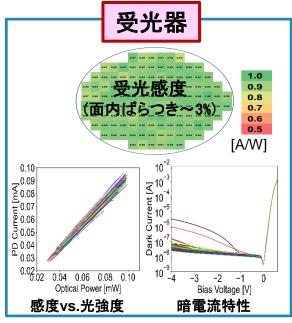

# 10Tbps/ノード可能性実証試作

#### 集積化プロセス技術

0.5 µm

# 10Tbps/ノードの高速光回路に集積される高機能光素子の特性改善・動作検証

変調器

#### 透過光強度(dB) リン注入 ハーフエッチ深さ 200nm 波長(nm) ボロン注入量 リン注入量 20 ハーフエッチ深さ 変調効率ばらつき(3σ) 光結合素子 注入位置ずれ 高精細アポダイズによる結合損失低減 6% (オーバーラップ) ファイバ 変調効率変化(%) -0.4dB低減 Coupling lo

回折格子

$2.7\pm0.1(3\sigma) dB$

# 合分波素子 低クロストーク・低ばらつきのフィルタ特性 ばらつき<2nm 8λ-AWG 8λ-AWG合分波器

Apodized

Uniform

プロセス感度解析に基づく変調器特性均一化

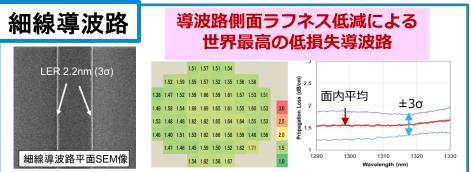

# 300mmー貫ファンドリへの展開

#### 集積化プロセス技術

# ファンドリにおいて集積プロセスを構築、集積デバイス動作の検証を完了

#### 細線導波路 プロセス最適化 1.5 1.0 (ラフネス低減) 細線導波路伝番損失面内分布 0.5 《440nm幅》。220nm高さ、Å=1550nm) ⇒低損失特性再現 0.0 [dB/cm] 伝搬損失(dB/cm) 0.0 0.1 伝搬損失(dB/cm) 0.0 0.1 C帯伝番損失 O帯伝番損失 0 0 420 440 460 480 320340360380400 導波路幅(nm) 導波路幅(nm) 伝番損失の導波路幅依存性

# 評価解析 -パラメータ抽出手法、デバイスモデル-

#### 集積化プロセス技術

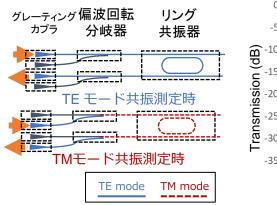

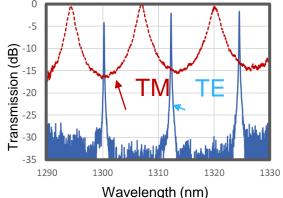

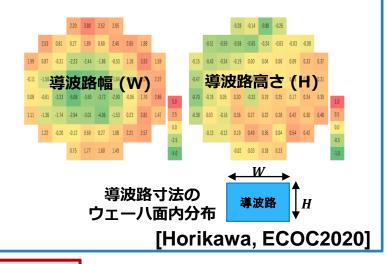

#### 高精度パラメータ抽出手法

リング共振器と偏波回転分岐器からなるモニタリング回路を用い、TEとTMの共振ピークを抽出に利用

導波路寸法シフトを高精度抽出(誤差:従来比 1/100)

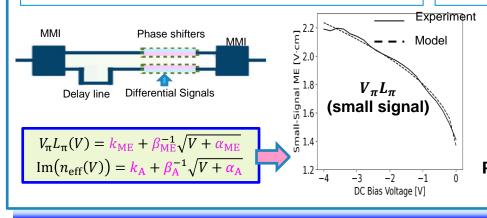

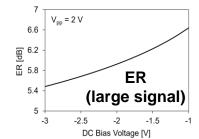

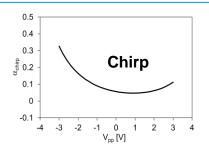

#### PN-MZI型変調器コンパクトモデル

#### 変調効率と吸収損失の非線形性を定式化

動作パラメータ(消光比、チャープ、変調信福等)を導出

PRBS信号入力時の消光比およびチャープ係数(モデル計算) [Murao, Opt. Commun. (2021)]

# ばらつきモデルを用いた高精度デバイス・回路設計

集積化プロセス技術

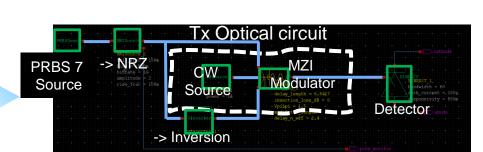

# ばらつきモデルを用いたトランシーバ設計検証

デバイスモデル、ばらつきモデルによる パラメータ抽出

ライブラリパラメータを用いたTx回路設計

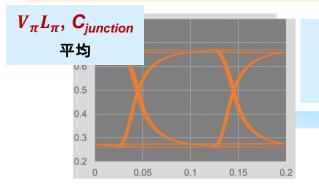

$V_{\pi}L_{\pi}$ ,  $C_{iunction}$ 平均 分散 共分散

#### パラメータ平均値を用いたシミュレーション

$V_{\pi}L_{\pi}$ ,  $C_{iunction}$ 分散 共分散

#### モンテカルロシミュレーション

設計・プロセス・検証のリンケージによる 高精度の光回路設計・プロセスプラットフォームを確立

$V_{\pi}L_{\pi}$ ,  $C_{junction}$ を確率乱数により変化 させ多数回のシミュレーションを試行

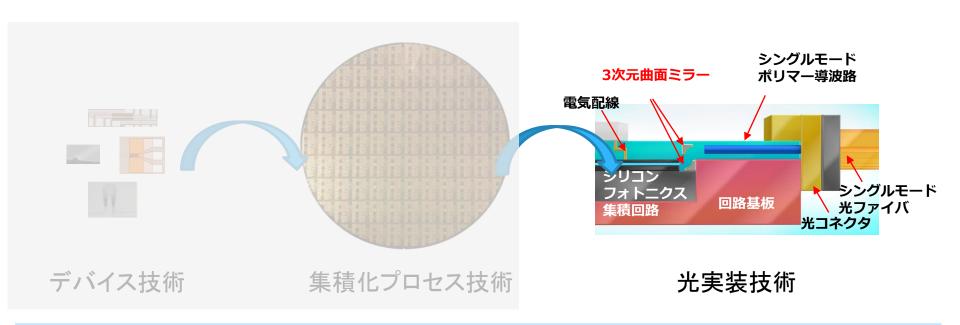

# 光実装技術

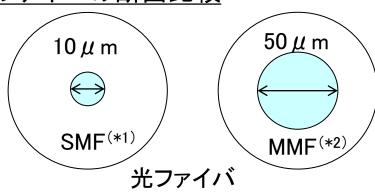

# シリフォト実用化の大きな課題: 光の入出力

#### 光実装技術

# 導波路と光ファイバの断面比較

$0.4\,\mu$  m

シリフォト 導波路

サブ $\mu$ mのシリフォト導波路 を10 $\mu$ m以上の光ファイバ に低コスト接続可能か課題

光ファイバ調芯で位置合わせ

#### <u>従来技術</u>

- 光信号を測定し、最適位置で固定するアクティブ 調芯を適用

- ➤ SMF接続はサブ µ mの位置制御が必要⇒時間がかかり高コスト

## 光信号

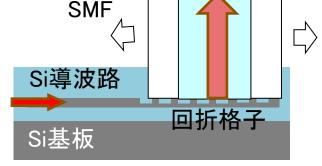

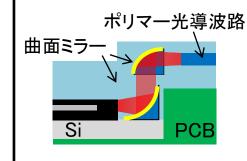

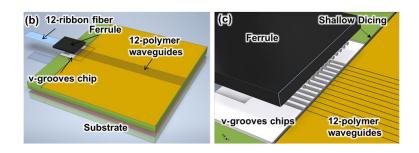

#### 1、2期(光I/Oコア)開発技術

光ピン(縦型ポリマー導波路)で光の幅を30 μ mに広げMMFに接続

(目合わせ精度10 µ mレベル⇒パッシブ実装)

光ピンは半導体プロセスと同じ露光技術形成

(\*1): シングルモードファイバ (\*2): マルチモードファイバ MMF 30 µ m 光信号 Si基板

# 光実装技術の開発目標

#### 光実装技術

#### 最終目標:

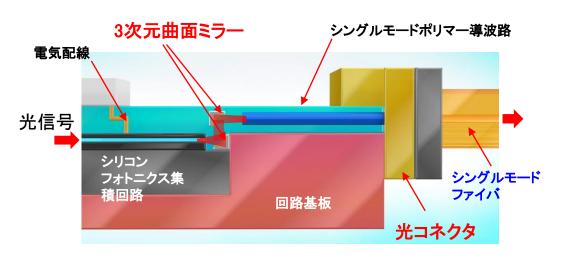

- ・16 波長多重に対応した波長偏波無依存な曲面ミラーをシリコンフォトニクスに集積

- ・上下曲面ミラーの高密度光結合20Tbps/mm<sup>2</sup>を実現

- ・光コネクタ用位置決め構造の高精度化と高精度実装技術を確立し、12芯光接続技術を実現

- ・マルチチップ実装技術、再配線技術、放熱構造技術を確立

10Tbps/ノード広帯域化実現に向け、波長多重技術を導入するため、

シングルモードファイバの入出力が必須

⇒高性能な高密度光結合(20Tbps/mm²)を実現するために3次元曲面ミラーを導入し 安価なパッシブ実装でシングルモードファイバを実装する

#### 【特徴】

- 接続スペースの最小化

- 光コネクタ数の低減と 回路基板への固定

# 光実装技術のアプローチ、特徴技術

#### 光実装技術

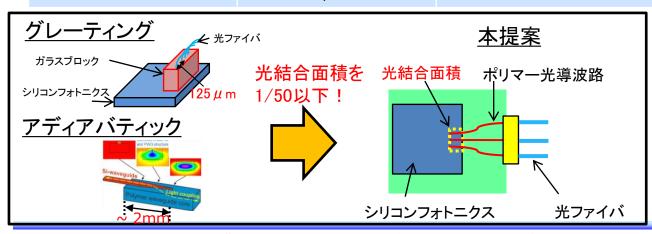

高性能な高密度光結合を実現するために新しい光結合手法(曲面ミラー)を提案

|                | グレーティング                 | アディアバティック                | 曲面ミラー(PETRA)                 |

|----------------|-------------------------|--------------------------|------------------------------|

| 光リンク<br>(実装方式) | ファイバダイレクト<br>(アクティブ実装)  | ポリマー導波路<br>(パッシブ実装)      | ポリマー導波路<br>(パッシブ実装)          |

| シリフォト結合器       | グレーティング                 | アディアバティック                | 曲面ミラー                        |

| 光結合面積          | △ ~10 mm <sup>2</sup>   | O ~2 mm <sup>2</sup>     |                              |

| IO密度 @100G/λ   | △ ~80 G/mm <sup>2</sup> | ○ ~600 G/mm <sup>2</sup> | © ~ 20T/mm <sup>2</sup> @16λ |

| 光結合損失          | O ~ 2 dB                | O ~ 1.5 dB               | 〇 目標< 1.5 dB                 |

| 波長無依存          | ×                       | 0                        | 0                            |

| 偏波無依存          | 2D:O,1D:×               | 0                        | 0                            |

# 3次元ミラーの作製方法

#### 光実装技術

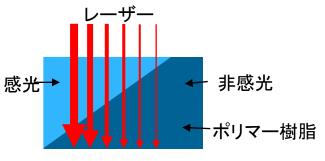

■ グレースケール露光を用いた3次元立体構造の作製

## レーザー描画を用いた曲面ミラー作製

レーザー強度で感光量を変え、 現像後にポリマー樹脂が立体化

- ・任意の3次元ミラーが作製可能となり、 高効率な光結合を実現

- ・露光プロセスで高精度な位置決めが可能 (上下ミラー、ポリマー光導波路)

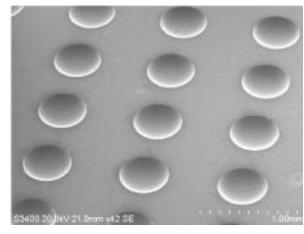

#### レンズ形状作製例

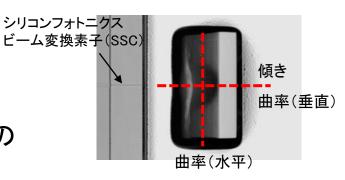

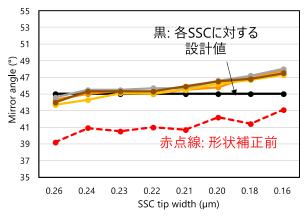

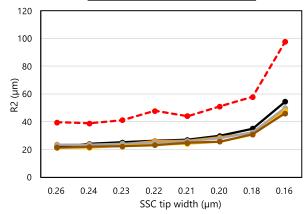

# 3次元ミラーの作製課題

#### 光実装技術

課題: 熱硬化(キュア)等のプロセス中に形状変化

形状変化を考慮したデザイン補正を行うことで所望の 構造を実現

#### <u>傾き</u>

#### 曲率半径(垂直方向)

#### 曲率半径(水平方向)

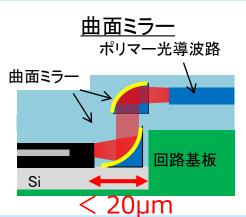

- ・8種類のシリコンSSCに対応した3次元ミラー構造(最小曲率半径:20µm)を作製

- 水平方向では±5.0%以下のばらつきを実現。垂直方向±25.8 %、角度方向±1.0% (ロス0.5dBの許容ばらつき範囲例: 曲率(水平)±21%、曲率(垂直)±23%、角度±1.1%。

※SSC tip 200nm width)

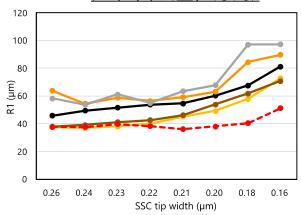

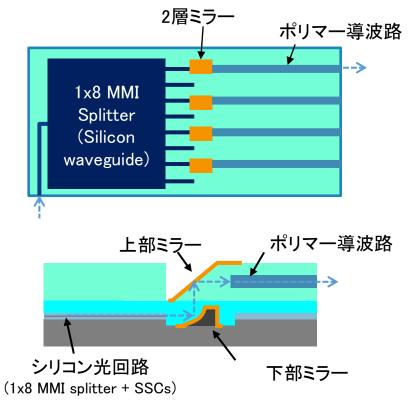

# 光電子集積インターポーザ基板の試作

#### 光実装技術

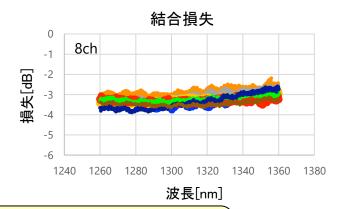

- 160nm先端幅のSSCを持つシリコン導波路に適した上下ミラーとポリマー光導波路 を集積した光電子集積インターポーザ基板を試作し、ミラー損失測定 ⇒上下ミラー(2.85dB)+ポリマー導波路(0.35dB)で3.2dBの低損失化を実現

- 85°Cまで良好な112Gbps伝送特性を実現

112-Gb/s PAM4 OSC EDFA PC Electrical 1545 nm LNM **EDFA AOP** substrate Optical Back-to-Back 25°C伝送結果 85°C伝送結果 TDECQ=1.40dB TDECQ=1.60 dB TDECQ=1.65 dB

85℃、112Gbps光リンク計測

光電子集積インタポーザ基板の構造図

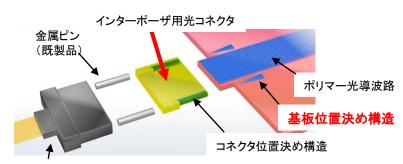

# 光電子集積インターポーザ用光コネクタ

#### 光実装技術

- 光電子集積インターポーザ用に2種類の光コネクタを検討

- 高信頼シリコンV溝コネクタ シリコンV溝を基板に埋め込み、それを目印 に導波路を製作

#### ■ 低コスト樹脂コネクタ

基板位置決め構造、コネクタ位置決め構造、 金属ピンが一直線となる機構

多芯光ファイバコネクタ(既製品)

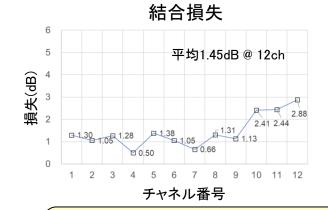

- シリコンV溝及び樹脂コネクタを用いて多芯光接続を実現

- シリコンV溝タイプでは平均<2dB@12chの接続損失を実現

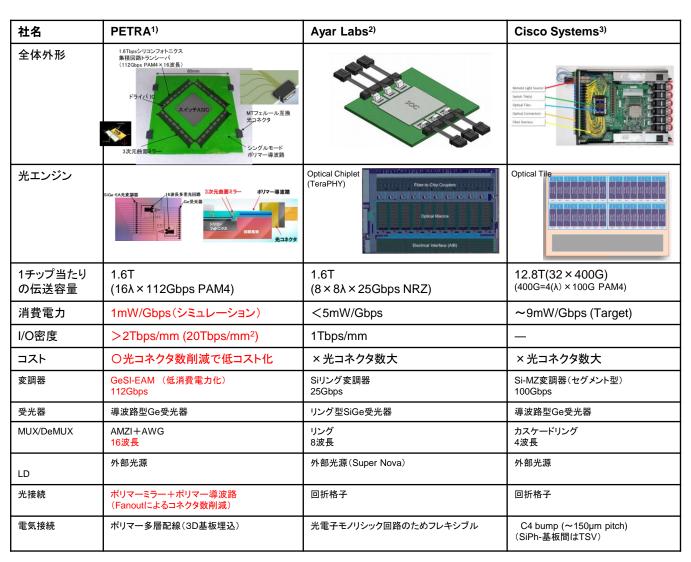

# 光電子集積インターポーザのベンチマーク

- PETRA、Ayar Labs、

Ciscoはシリフォト集積

チップをタイル方式で

LSIチップの周辺に配置

する方式

- 消費電力の削減とI/O 密度の増大が重要。 更に、光ファイバー数増 加に伴う、接続問題の 解決が重要になる。

1)中村, 電子情報通信学会論文誌C, vol. J104-C, No. 8, pp. 1-7, 2021.

<sup>2)</sup>M. Wade, HotChips 2019.

<sup>3)</sup>B. Welch, EPIC Online Technology Meeting on Co-Packaged Optics, 2020.

# まとめ

#### デバイス技術

- 光変調器、受光器及びこれらを駆動する電子回路の112Gbps PAM4動作を実証した。

- 16波長を合分波可能な波長多重フィルタを開発し、低損失、低クロストーク特性を実証した。

- 22nm CMOSを用いた解析で1mW/Gbpsの低消費電力化の目途を得た。

## 集積プロセス技術

- 300mm統合プロセスを確立し、これを用いた10Tbps/ノード可能性実証試作を完了した。

- 集積プロセスの一貫試作ファンドリへの展開を完了した。

- ウエハプローバを用いた設計・プロセス統合ライブラリを構築し、ばらつきモデルによる 設計・プロセスの高信頼化を実現した。

#### 光実装技術

- 3次元ミラーを用いて光電子集積インターポーザを試作し、シリフォト光入出力密度 20Tbps/mm²と10Tbps 伝送密度の光リンクを実証した。

- シングルモードポリマー光導波路アレイとシングルモード光ファイバアレイの12芯高精度 光結合(平均〈2dB)を実証した。

以上より、プロジェクト目標を全て達成した。